来源:壹芯微 发布日期

2020-12-15 浏览:-

来源:壹芯微 发布日期

2020-12-15 浏览:-MOS管知识解析|要如何降低MOS的失效率

如何以最小代价降低MOS的失效率

如何降低MOS的失效率:在高端MOS的栅极驱动电路中,自举电路因技术简单、成本低廉得到了广泛的应用。然而在实际应用中,MOS常莫名其妙的失效,有时还伴随着驱动IC的损坏。如何解决?一个合适的电阻就可搞定问题。

【问题分析】

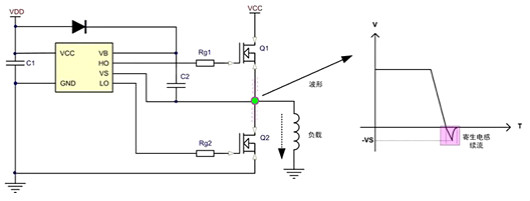

图为典型的半桥自举驱动电路,由于寄生电感的存在,在高端MOS关闭后,低端MOS的体二极管钳位之前,寄生电感通过低端二极管进行续流,导致VS端产生负压,且负压的大小与寄生电感与成正比关系。

该负压会把驱动的电位拉到负电位,导致驱动电路异常,还可能让自举电容过充电导致驱动电路或者栅极损坏。由于IC的驱动端通常都有寄生二极管,当瞬间的大电流流过驱动口的二极管时,很可能引发寄生SCR闭锁效应,导致驱动电路彻底损坏。

【解决方法】

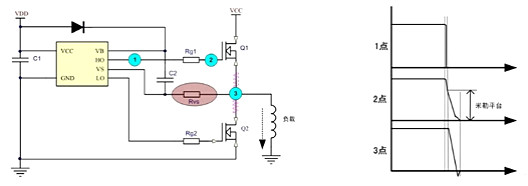

如何降低MOS的失效率:如上图所示,在自举驱动芯片VS端与Q1的源极之间增加一个电阻Rvs,该电阻不仅是自举限流电阻,同时还是导通电阻和关断电阻。

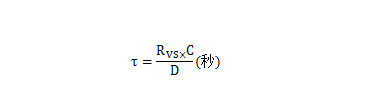

由于占空比受自举电容影响,该电阻值一般不能取得较大,推荐值为3~10Ω较为适宜。电阻和自举电容的容值与其充电时间可以由以下公式得出:

其中C是自举电容容值,D为最大占空比

对于减小高端MOS驱动的寄生振荡,除通过增加驱动端的电阻发挥作用外,在印制电路板的设计中,还可注意以下一些细节,将寄生振荡降到最低。

如:自举二极管应紧靠自举电容,功率布线尽量短且走线圆滑,直插器件应紧贴PCB以减小寄生电感等。

壹芯微科技针对二三极管,MOS管作出了良好的性能测试,应用各大领域,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍

工厂地址:安徽省六安市金寨产业园区

深圳办事处地址:深圳市福田区宝华大厦A1428

中山办事处地址:中山市古镇长安灯饰配件城C栋11卡

杭州办事处:杭州市西湖区文三西路118号杭州电子商务大厦6层B座

电话:13534146615

企业QQ:2881579535

深圳市壹芯微科技有限公司 版权所有 | 备案号:粤ICP备2020121154号