分段DAC

当我们需要设计一个具有特定性能的DAC时,很可能没有任何一种架构是理想的。这种情况下,可以将两个或更多DAC组合成一个更高分辨率的DAC,以获得所需的性能。这些DAC可以是同一类型,也可以是不同类型,各DAC的分辨率无需相同。

原则上,一个DAC处理MSB,另一个DAC处理LSB,其输出以某种方式相加。这一过程称为“分段”,这些更复杂的结构称为“分段DAC”。有许多不同类型的分段DAC,本指南不可能逐一说明,但会介绍其中的几种。

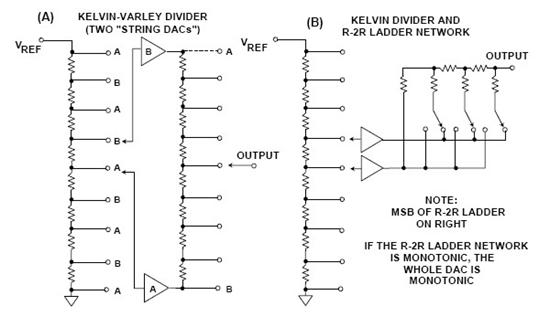

图1显示了两类分段电压输出DAC。图1A中的架构有时称为Kelvin-Varley分压器,由两个或更多“串DAC”组成。第一级与第二级之间存在缓冲器,因此第二个串DAC不会加载第一个串DAC,该串中的电阻值无需与另一个串中的电阻值相同。然而,各串中的所有电阻必须彼此相等,否则DAC将不是线性的。示例的第一级和第二级均为3位,但为了具有普遍意义,我们称第一(MSB)级的分辨率为M位,第二(LSB)级的分辨率为K位,总分辨率为N = M + K位。MSB DAC具有2M个等值电阻,LSB DAC具有2K个等值电阻。

图1:分段式电压-输出DAC

当然,缓冲放大器具有失调,这可能会在缓冲分段串DAC中造成非单调性。在缓冲Kelvin-Varley分压器缓冲器的更简单配置中(图1A),缓冲器A总是“低于”(电位低于)缓冲器B,LSB串DAC上标“A”的额外抽头是不必要的。数据解码电路仅为两个优先级编码器。然而,在此配置中,缓冲器失调可能会造成非单调性。

但是,如果将MSB串DAC的解码电路做得更复杂一点,使得缓冲器A只能连接到MSB串DAC标“A”的抽头,缓冲器B只能连接到标“B”的抽头,则缓冲器失调将无法造成非单调性。当然,LSB串DAC解码必须改变方向, 缓冲器需要跳跃连接到另一端,LSB串DAC的抽头A和B不需要交替,但这需要略微复杂一点的逻辑,而性能的提高证明这样做是值得的。

也可以不使用第二个电阻串,而是使用一个二进制DAC来产生三个LSB,如图1B所示。制造极高分辨率的R-2R梯形电阻网络非常困难,更确切地说,很难将其调整为单调性。因此,常见的情况是LSB使用由梯形电阻网络,2到5个MSB则使用其它结构来合成高分辨率DAC。图1B所示的电压输出DAC由一个3位串DAC和一个3位缓冲电压模式梯形电阻网络组成。

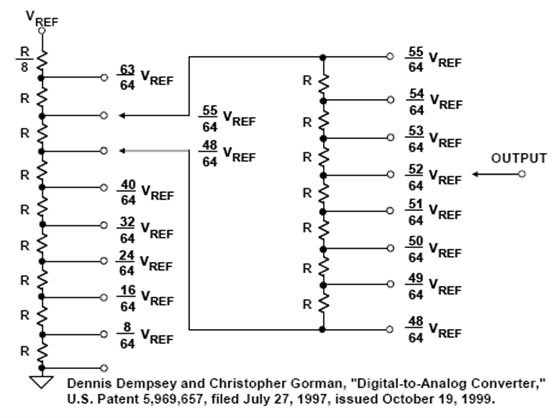

图2:分段无缓冲串DAC使用专利架构

无缓冲的分段串DAC架构如图2所示。在原理上,这种形式更巧妙,并且可以通过CMOS工艺制造(它能制造电阻和开关,但不能制造放大器),因此也更便宜。这种架构本身即具备单调性。

本例中,两个串中的电阻必须等值,唯一的例外是MSB串中的顶端电阻必须较小(其它电阻值的1/2K),此外LSB串具有2K – 1个电阻,而不是2K个。由于没有缓冲器,LSB串看起来像是与它切换并加载的MSB串中的电阻并联,这就使得该MSB电阻上的电压降低LSB串 DAC的1 LSB,而这正是所需要的结果。由于无缓冲,此DAC的输出阻抗随着数字代码的改变而变化。

肖特基二极管MBR2045CT参数

肖特基二极管MBR2045CT参数 三极管S8050参数

三极管S8050参数 整流二极管SS34参数

整流二极管SS34参数 超快恢复二极管ES1JF参数

超快恢复二极管ES1JF参数