来源:壹芯微 发布日期

2020-05-12 浏览:-

来源:壹芯微 发布日期

2020-05-12 浏览:-5G时代的集成电路封装技术-SiP封装资料

SiP(系统级封装,System in Package)是在系统芯片(SoC)设计理念基础发展出来的一种集成电路封装技术,指将多颗芯片或单芯片与电阻器、电容器、连接器、晶振、天线等被动组件封装在一起,构成更为一个具有一定功能的电路系统。

SIP对不同芯片、电子元件进行并排或叠加形成单个标准封装

从一定程度讲,SiP是SoC技术在纳米时代的裂变。随着SoC制程从微米进入纳米,单一集成电路芯片内所能容纳的晶体管数目愈来愈多,业界通过提高SoC整合度满足用户对低功耗、低成本及高效能的要求。但是当半导体制程进入纳米时代后,SoC所面临的各种问题,如制程微缩瓶颈,成本愈来愈大,异质(Heterogeneous)整合困难,产品生命周期变短等,这为SiP技术带来了崭新的发展机会。

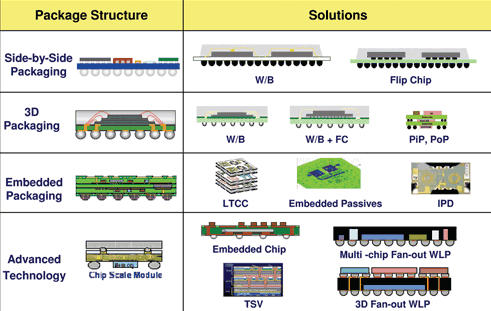

概念上,SiP包括了多芯片模组(Multi-chip Module;MCM)技术、多芯片封装(Multi-chip Package;MCP)技术、芯片堆叠(Stack Die)、PoP(Package on Package)、PiP(Package in Package),以及将主/被动组件内埋于基板(Embedded Substrate)等技术。

在结构上,MCM属于二维的2D构装,而MCP、Stack Die、PoP、PiP等则属于立体的3D构装;由于3D更能符合小型化、高效能等需求,因而在近年来备受业界青睐。

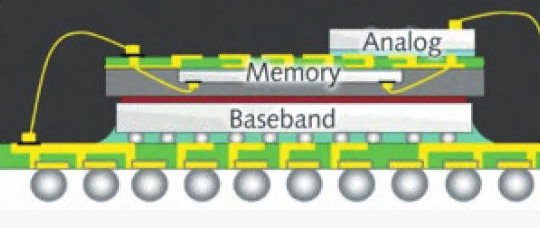

工艺上,SiP集成电路封装互连技术(Interconnection)多以打线接合(Wire Bonding)为主,少部分还采用覆晶技术(Flip Chip),或是Flip Chip搭配Wire Bonding作为与Substrate(IC载板)间的互连。但以Stack Die(堆叠芯片)为例,上层的芯片仍需藉由Wire Bonding来连接,当堆叠的芯片数增加,越上层的芯片所需的Wire Bonding长度则将越长,也因此影响了整个系统的效能;而为了保留打线空间的考虑,芯片与芯片间则需适度的插入Interposer,造成封装厚度的增加。

SiP技术特点

系统封装(SiP)技术在现有集成电路封装中并非高困难度的制程,因为各种功能芯片利用集成电路封装技术整合,除考虑封装体的散热处理外,功能芯片组构可以将原本离散的功能设计或组件,整合在单一芯片,不仅可以避免设计方案被抄袭复制,也能透过多功能芯片整合的优势让最终产品更具市场竞争力,尤其在产品的体积、功耗与成本上都能因为SiP技术而获得改善。

最基础的SIP封装结构

SiP元器件若设计规划得当,已可相当于一系统载板的相关功能芯片、电路的总和,而依据不同的功能芯片进行系统封装,可以采简单的Side by Side芯片布局,也可利用相对更复杂的多芯片模组MCM(Multi-chip Module)技术、多芯片封装MCP(Multi-chip Package)技术、芯片堆叠(Stack Die)、PoP(Package on Package)、PiP(Package in Package)等不同难度与制作方式进行系统组构。也就是说,在单一个封装体内不只可运用多个芯片进行系统功能建构,甚至还可将包含前述不同类型器件、被动组件、电路芯片、功能模组封装进行堆叠,透过内部连线或是更复杂的3D IC技术整合,构建成更为复杂的、完整的SiP系统功能。

而在SiP整合封装中,关键的技术就在于SiP封装体中的芯片或功能模组的芯片内互连技术(Interconnection),在一般简单形式或是对芯片体积要求不高的方案中,运用打线接合(Wire Bonding)即可满足多数需求,而打线接合形式芯片多用Side by Side并列布局为主,当功能芯片数量多时,芯片的占位面积就会增加,而若要达到SiP封装体再积极微缩设计,就可改用技术层次更高的覆晶技术(Flip Chip)或是Flip Chip再搭配打线接合与IC载板(Substrate)之间进行互连。

基本上堆叠芯片(Stack Die)的作法在上层的芯片或模块仍然需要透过打线接合进行连接,但若碰到SiP的整合芯片、功能模块数量较多时,即堆叠的芯片、功能模组数量增加,这会导致越是设于SiP结构上层的芯片、模块所需要的打线连接电子线路长度将因此增长,传输线路拉长对于高时脉运作的功能模块会产生线路杂讯或是影响了整体系统效能;至于SiP在结构上为了预留Wire Bonding的打线空间,对芯片与芯片或是功能模块与功能模块间插入的Interposer处理,也会因为这些必要程序导致SiP最终封装成品的厚度增加。

典型SiP封装方案

随着集成电路封装技术不断演进,芯片或功能模块的裸晶本身制程,已从微米制程升级至纳米等级,这代表单一个功能芯片或功能模块可以越做越小,也代表SiP的功能可因而得到倍数的成长,甚至还能游刃有余地维持相同的封装体尺寸。

SiP应用优势

目前,SiP封装已经成为轻薄电子产品首选的集成电路封装形式。

首先,SiP可利用封装技术让整合设计更具效率,也就是说SiP可在单一封装体内装多组功能芯片,例如单一SiP若整合两组功能芯片,使用堆叠设计可以在相同芯片占位面积设置双芯片功能,若是三个功能芯片构装,则可以在单一芯片略大的体积设置多芯片功能。

其次,SiP构装芯片的设计验证会比同样多功能芯片整合的SoC设计方案更简单许多,基本上这些功能独立的芯片皆已可透过既有的验证流程确认功能完整性,而在SiP制程中仅针对芯片与芯片、功能模块与功能模块的内部连线在封装后是否正常无误进行验证,大幅减少设计流程与验证成本。

而SoC却需要透过版图布局/布线,不仅在设计流程与负荷相对复杂,在后期的芯片验证调校成本也相对较高,两者相较SiP在争取产品上市时间有绝对优势。同时,SiP的优点还有可以结合不同功能芯片、功能模块,在面对异质芯片构装方面可以极具弹性,在封装体内还可设置被动组件,甚至集成天线模块进封装体,芯片的封装成果可以自成一套电子系统,实现嵌入式无源组件的设计方案组合。

第三,SiP也可大幅减低系统开发成本,因为相关的电子回路都可以透过封装体内的线路与组件布局进行整合,如此一来不仅节省了SiP终端元器件本身的占位空间,也能把部分电路载板的关键线路、零组件并入SiP封装体中,极度简化PCB电路板的复杂度与面积,成本与验证程序可获得大幅优化。

另外,高度集成电路封装整合提升产品抗机械、抗化学腐蚀能力SiP也具备极好的抗机械、抗化学腐蚀能力,因为相关电路都以封装体整个包覆起来,可增加电路载板的抗机械应力、抗化学腐蚀能力,同时提高了电子系统的可靠性。

SiP封装产业

全球主要集成电路封装大厂中,日月光早在2010年发展SiP技术,并代工苹果公司得到Wi-Fi、处理器、指纹辨识、压力触控、MEMS等模组订单。此外,日月光也与DRAM制造大厂华亚科策略联盟共同发展SiP范畴的TSV 2.5D IC技术,也与日本基板厂商TDK合作成立子公司日月旸,生产积体电路内埋式基板,将更多的感测器与射频组件等芯片整合在尺寸更小的基板上。

由于轻薄短小、多功能、低功耗是智能终端产品的大趋势,特别是在5G智能手机等终端产品的带动,SiP封装产品的市场需求将会不断提升。作为世界5G产品基地,中国市场将是SiP封装的主要成长动力。

壹芯微科技针对二三极管,MOS管作出了良好的性能测试,应用各大领域,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍

工厂地址:安徽省六安市金寨产业园区

深圳办事处地址:深圳市福田区宝华大厦A1428

中山办事处地址:中山市古镇长安灯饰配件城C栋11卡

杭州办事处:杭州市西湖区文三西路118号杭州电子商务大厦6层B座

电话:13534146615

企业QQ:2881579535

深圳市壹芯微科技有限公司 版权所有 | 备案号:粤ICP备2020121154号