MOSFETs Silicon N-channel MOS (U-MOSVIII-H)

# TK22A10N1

#### 1. Applications

• Switching Voltage Regulators

#### 2. Features

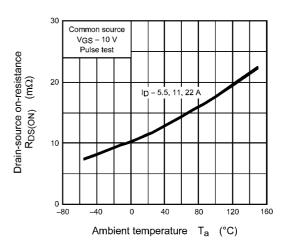

- (1) Low drain-source on-resistance:  $R_{DS(ON)} = 11.5 \text{ m}\Omega$  (typ.) ( $V_{GS} = 10 \text{ V}$ )

- (2) Low leakage current:  $I_{DSS} = 10 \mu A \text{ (max) (V}_{DS} = 100 \text{ V)}$

- (3) Enhancement mode:  $V_{th}$  = 2.0 to 4.0 V ( $V_{DS}$  = 10 V,  $I_{D}$  = 0.3 mA)

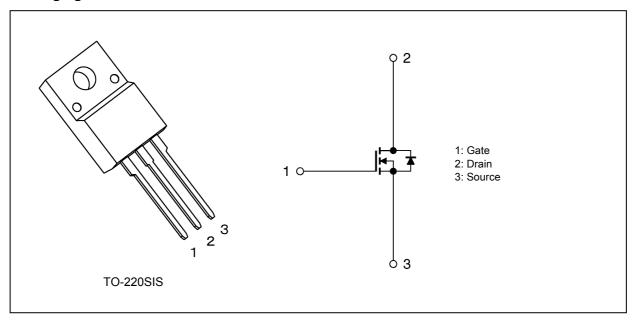

### 3. Packaging and Internal Circuit

# 4. Absolute Maximum Ratings (Note) (Ta = 25°C unless otherwise specified)

| Characterist                  | Symbol                  | Rating     | Unit             |            |    |

|-------------------------------|-------------------------|------------|------------------|------------|----|

| Drain-source voltage          |                         |            | $V_{DSS}$        | 100        | V  |

| Gate-source voltage           |                         |            | V <sub>GSS</sub> | ±20        |    |

| Drain current (DC)            | (Silicon limit)         | (Note 1,2) | I <sub>D</sub>   | 52         | Α  |

| Drain current (DC)            | (T <sub>c</sub> = 25°C) | (Note 1)   | I <sub>D</sub>   | 22         |    |

| Drain current (pulsed)        | (t = 1 ms)              | (Note 1)   | I <sub>DP</sub>  | 102        |    |

| Power dissipation             | (T <sub>c</sub> = 25°C) |            | $P_{D}$          | 30         | W  |

| Single-pulse avalanche energy |                         | (Note 3)   | E <sub>AS</sub>  | 48         | mJ |

| Avalanche current             |                         |            | I <sub>AR</sub>  | 22         | Α  |

| Channel temperature           |                         |            | T <sub>ch</sub>  | 150        | °C |

| Storage temperature           |                         |            | T <sub>stg</sub> | -55 to 150 |    |

Note: Using continuously under heavy loads (e.g. the application of high temperature/current/voltage and the significant change in temperature, etc.) may cause this product to decrease in the reliability significantly even if the operating conditions (i.e. operating temperature/current/voltage, etc.) are within the absolute maximum ratings.

Please design the appropriate reliability upon reviewing the Toshiba Semiconductor Reliability Handbook ("Handling Precautions"/"Derating Concept and Methods") and individual reliability data (i.e. reliability test report and estimated failure rate, etc).

### 5. Thermal Characteristics

| Characteristics                       | Symbol                | Max  | Unit |

|---------------------------------------|-----------------------|------|------|

| Channel-to-case thermal resistance    | R <sub>th(ch-c)</sub> | 4.16 | °C/W |

| Channel-to-ambient thermal resistance | R <sub>th(ch-a)</sub> | 62.5 |      |

Note 1: Ensure that the channel temperature does not exceed 150°C.

Note 2: Limited by silicon chip capability.

Note 3:  $V_{DD}$  = 80 V,  $T_{ch}$  = 25°C (initial), L = 77.6  $\mu H,\,R_{G}$  = 1.2  $\Omega,\,I_{AR}$  = 22 A

Note: This transistor is sensitive to electrostatic discharge and should be handled with care.

#### 6. Electrical Characteristics

# 6.1. Static Characteristics (T<sub>a</sub> = 25°C unless otherwise specified)

| Characteristics                         | Symbol               | Test Condition                                    | Min | Тур. | Max  | Unit |

|-----------------------------------------|----------------------|---------------------------------------------------|-----|------|------|------|

| Gate leakage current                    | I <sub>GSS</sub>     | $V_{GS} = \pm 20 \text{ V}, V_{DS} = 0 \text{ V}$ | _   | _    | ±0.1 | μΑ   |

| Drain cut-off current                   | I <sub>DSS</sub>     | V <sub>DS</sub> = 100 V, V <sub>GS</sub> = 0 V    | _   | -    | 10   |      |

| Drain-source breakdown voltage          | V <sub>(BR)DSS</sub> | I <sub>D</sub> = 10 mA, V <sub>GS</sub> = 0 V     | 100 | _    | _    | V    |

| Drain-source breakdown voltage (Note 4) | V <sub>(BR)DSX</sub> | I <sub>D</sub> = 10 mA, V <sub>GS</sub> = -20 V   | 65  | _    | _    |      |

| Gate threshold voltage                  | V <sub>th</sub>      | V <sub>DS</sub> = 10 V, I <sub>D</sub> = 0.3 mA   | 2.0 | _    | 4.0  |      |

| Drain-source on-resistance              | R <sub>DS(ON)</sub>  | V <sub>GS</sub> = 10 V, I <sub>D</sub> = 11 A     | _   | 11.5 | 13.8 | mΩ   |

Note 4: If a reverse bias is applied between gate and source, this device enters  $V_{(BR)DSX}$  mode. Note that the drain-source breakdown voltage is lowered in this mode.

# 6.2. Dynamic Characteristics (T<sub>a</sub> = 25°C unless otherwise specified)

| Characteristics                | Symbol           | Test Condition                                           | Min | Тур. | Max | Unit |

|--------------------------------|------------------|----------------------------------------------------------|-----|------|-----|------|

| Input capacitance              | C <sub>iss</sub> | V <sub>DS</sub> = 50 V, V <sub>GS</sub> = 0 V, f = 1 MHz | _   | 1800 |     | pF   |

| Reverse transfer capacitance   | C <sub>rss</sub> |                                                          |     | 18   |     |      |

| Output capacitance             | C <sub>oss</sub> |                                                          |     | 310  |     |      |

| Gate resistance                | r <sub>g</sub>   | _                                                        | _   | 2.0  | _   | Ω    |

| Switching time (rise time)     | t <sub>r</sub>   | See Figure 6.2.1                                         |     | 11   |     | ns   |

| Switching time (turn-on time)  | t <sub>on</sub>  |                                                          |     | 27   |     |      |

| Switching time (fall time)     | t <sub>f</sub>   |                                                          | _   | 11   |     |      |

| Switching time (turn-off time) | t <sub>off</sub> |                                                          | _   | 38   |     |      |

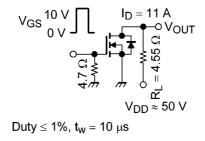

Fig. 6.2.1 Switching Time Test Circuit

# 6.3. Gate Charge Characteristics (T<sub>a</sub> = 25°C unless otherwise specified)

| Characteristics                                 | Symbol           | Test Condition                                                           | Min | Тур. | Max | Unit |

|-------------------------------------------------|------------------|--------------------------------------------------------------------------|-----|------|-----|------|

| Total gate charge (gate-source plus gate-drain) | $Q_g$            | $V_{DD} \approx 80 \text{ V}, V_{GS} = 10 \text{ V}, I_D = 22 \text{ A}$ | _   | 28   |     | nC   |

| Gate-source charge 1                            | Q <sub>gs1</sub> |                                                                          | _   | 8.7  |     |      |

| Gate-drain charge                               | $Q_{gd}$         |                                                                          | _   | 8.1  | _   |      |

| Gate switch charge                              | $Q_{SW}$         |                                                                          | _   | 12   | _   |      |

### 6.4. Source-Drain Characteristics (Ta = 25°C unless otherwise specified)

| Characteristics                |          | Symbol           | Test Condition                                | Min | Тур. | Max  | Unit |

|--------------------------------|----------|------------------|-----------------------------------------------|-----|------|------|------|

| Reverse drain current (DC)     | (Note 5) | I <sub>DR</sub>  | _                                             | _   | _    | 22   | Α    |

| Reverse drain current (pulsed) | (Note 5) | I <sub>DRP</sub> | _                                             | _   | _    | 102  |      |

| Diode forward voltage          |          | V <sub>DSF</sub> | I <sub>DR</sub> = 22 A, V <sub>GS</sub> = 0 V | _   | _    | -1.2 | V    |

| Reverse recovery time          | (Note 6) | t <sub>rr</sub>  | I <sub>DR</sub> = 22 A, V <sub>GS</sub> = 0 V | _   | 54   | _    | ns   |

| Reverse recovery charge        | (Note 6) | Q <sub>rr</sub>  | -dl <sub>DR</sub> /dt = 100 A/μs              | _   | 94   |      | nC   |

Note 5: Ensure that the channel temperature does not exceed 150°C.

Note 6: Ensure that V<sub>DS</sub> peak does not exceed V<sub>DSS</sub>.

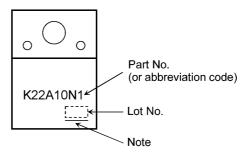

#### 7. Marking (Note)

Fig. 7.1 Marking

Note: A line under a Lot No. identifies the indication of product Labels.

Not underlined: [[Pb]]/INCLUDES > MCV

Underlined: [[G]]/RoHS COMPATIBLE or [[G]]/RoHS [[Pb]]

Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product.

The RoHS is the Directive 2002/95/EC of the European Parliament and of the Council of 27 January 2003 on the restriction of the use of certain hazardous substances in electrical and electronic equipment.

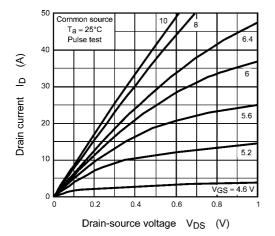

### 8. Characteristics Curves (Note)

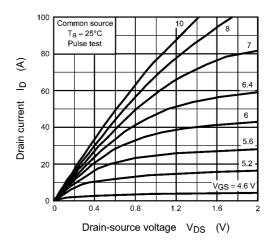

Fig. 8.1  $I_D - V_{DS}$

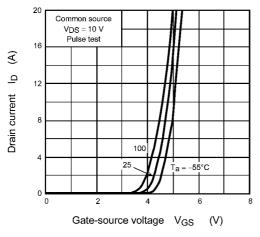

Fig. 8.3 I<sub>D</sub> - V<sub>GS</sub>

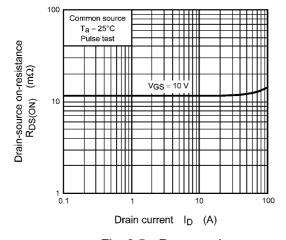

Fig. 8.5 R<sub>DS(ON)</sub> - I<sub>D</sub>

Fig. 8.2 I<sub>D</sub> - V<sub>DS</sub>

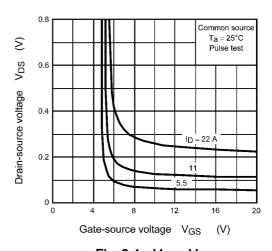

Fig. 8.4 V<sub>DS</sub> - V<sub>GS</sub>

Fig. 8.6 R<sub>DS(ON)</sub> - T<sub>a</sub>