## **STW14NM50**

# N-CHANNEL 550V @ Tjmax - 0.32Ω - 14A TO-247 MDmesh™ MOSFET

**Table 1: General Features**

| TYPE      | V <sub>DSS</sub><br>(@Tjmax) | R <sub>DS(on)</sub> | I <sub>D</sub> |

|-----------|------------------------------|---------------------|----------------|

| STW14NM50 | 550 V                        | < 0.35 Ω            | 14 A           |

- TYPICAL  $R_{DS}(on) = 0.32 \Omega$

- HIGH dv/dt AND AVALANCHE CAPABILITIES

- 100% AVALANCHE RATED

- LOW INPUT CAPACITANCE AND GATE CHARGE

- LOW GATE INPUT RESISTANCE

- TIGHT PROCESS CONTROL AND HIGH MANUFACTORING YIELDS

#### **DESCRIPTION**

The MDmesh™ is a new revolutionary MOSFET technology that associates the Multiple Drain process with the Company's PowerMESH™ horizontal layout. The resulting product has an outstanding low on-resistance, impressively high dv/dt and excellent avalanche characteristics. The adoption of the Company's proprierati strip technique yields overall dynamic performance that is significantly better than that of similar completition's products.

#### **APPLICATIONS**

The MDmesh<sup>™</sup> family is very suitablr for increase the power density of high voltage converters allowing system miniaturization and higher efficiencies.

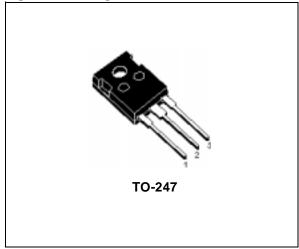

Figure 1: Package

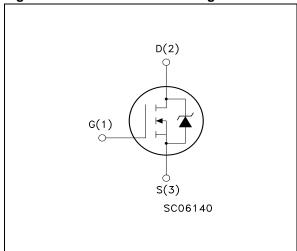

Figure 2: Internal Schematic Diagram

**Table 2: Order Codes**

| SALES TYPE | SALES TYPE MARKING |        | PACKAGING |  |

|------------|--------------------|--------|-----------|--|

| STW14NM50  | W14NM50            | TO-247 | TUBE      |  |

**Table 3: Absolute Maximum ratings**

| Symbol                         | Parameter                                            | Value      | Unit |

|--------------------------------|------------------------------------------------------|------------|------|

| V <sub>GS</sub>                | Gate- source Voltage                                 | ±30        | V    |

| I <sub>D</sub>                 | Drain Current (continuous) at T <sub>C</sub> = 25°C  | 14         | А    |

| I <sub>D</sub>                 | Drain Current (continuous) at T <sub>C</sub> = 100°C | 8.8        | Α    |

| I <sub>DM</sub> <sup>(1)</sup> | Drain Current (pulsed)                               | 56         | А    |

| P <sub>TOT</sub>               | Total Dissipation at T <sub>C</sub> = 25°C           | 175        | W    |

|                                | Derating Factor                                      | 1.28       | W/°C |

| dv/dt                          | Peak Diode Recovery voltage slope                    | 6          | V/ns |

| T <sub>stg</sub>               | Storage Temperature                                  | -65 to 150 | °C   |

| Tj                             | Max. Operating Junction Temperature                  | 150        | °C   |

<sup>(•)</sup>Pulse width limited by safe operating area

### **Table 4: Thermal Data**

| Rthj-case      | Thermal Resistance Junction-case Max           | 0.715 | °C/W |

|----------------|------------------------------------------------|-------|------|

| Rthj-amb       | Thermal Resistance Junction-ambient Max        | 30    | °C/W |

| T <sub>I</sub> | Maximum Lead Temperature For Soldering Purpose | 300   | °C   |

### **Table 5: Avalanche Characteristics**

| Symbol          | Parameter                                                                                | Max Value |    |

|-----------------|------------------------------------------------------------------------------------------|-----------|----|

| I <sub>AR</sub> | Avalanche Current, Repetitive or Not-Repetitive (pulse width limited by $T_j$ max)       | 12        | А  |

| E <sub>AS</sub> | Single Pulse Avalanche Energy (starting $T_j = 25$ °C, $I_D = I_{AR}$ , $V_{DD} = 50$ V) | 400       | mJ |

# **ELECTRICAL CHARACTERISTICS** (T<sub>CASE</sub> =25°C UNLESS OTHERWISE SPECIFIED)

### Table 6: On /Off

| Symbol               | Parameter                                                | Test Conditions                                                 | Min. | Тур. | Max.    | Unit     |

|----------------------|----------------------------------------------------------|-----------------------------------------------------------------|------|------|---------|----------|

| V <sub>(BR)DSS</sub> | Drain-source Breakdown<br>Voltage                        | $I_D = 250 \mu A, V_{GS} = 0$                                   | 500  |      |         | V        |

| I <sub>DSS</sub>     | Zero Gate Voltage<br>Drain Current (V <sub>GS</sub> = 0) | $V_{DS}$ = Max Rating<br>$V_{DS}$ = Max Rating, $T_{C}$ = 125°C |      |      | 1<br>10 | μA<br>μA |

| I <sub>GSS</sub>     | Gate-body Leakage<br>Current (V <sub>DS</sub> = 0)       | V <sub>GS</sub> = ± 30 V                                        |      |      | ± 100   | nA       |

| V <sub>GS(th)</sub>  | Gate Threshold Voltage                                   | $V_{DS} = V_{GS}, I_{D} = 250 \mu A$                            | 3    | 4    | 5       | V        |

| R <sub>DS(on</sub>   | Static Drain-source On Resistance                        | V <sub>GS</sub> = 10 V, I <sub>D</sub> = 6 A                    |      | 0.32 | 0.35    | Ω        |

<sup>(\*)</sup>Limited only by maximum temperature allowed

$<sup>(1)</sup>I_{SD} \leq 14A, \ di/dt \leq 100A/\mu s, \ V_{DD} \leq V_{(BR)DSS}, \ T_j \leq T_{JMAX}.$

### **ELECTRICAL CHARACTERISTICS (CONTINUED)**

### **Table 7: Dynamic**

| Symbol                                                                                               | Parameter                                                           | Test Conditions                                                                                             | Min. | Тур.                | Max. | Unit                 |

|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------|---------------------|------|----------------------|

| g <sub>fs</sub> (1)                                                                                  | Forward Transconductance                                            | $V_{DS} > I_{D(on)} \times R_{DS(on)max},$<br>$I_{D} = 6A$                                                  |      | 5.2                 |      | S                    |

| C <sub>iss</sub><br>C <sub>oss</sub><br>C <sub>rss</sub>                                             | Input Capacitance Output Capacitance Reverse Transfer Capacitance   | $V_{DS} = 25 \text{ V, f} = 1 \text{ MHz,} $<br>$V_{GS} = 0$                                                |      | 1000<br>180<br>25   |      | pF<br>pF<br>pF       |

| Coss eq (3).                                                                                         | Equivalent Output<br>Capacitance                                    | V <sub>GS</sub> = 0 V, V <sub>DS</sub> = 0 to 400 V                                                         |      | 90                  |      | pF                   |

| R <sub>G</sub>                                                                                       | Gate Input Resistance                                               | f=1 MHz Gate DC Bias = 0<br>Test Signal Level = 20mV<br>Open Drain                                          |      | 1.6                 |      | Ω                    |

| $\begin{array}{c} t_{\text{d(on)}} \\ t_{\text{r}} \\ t_{\text{d(off)}} \\ t_{\text{f}} \end{array}$ | Turn-on Delay Time<br>Rise Time<br>Turn-off-Delay Time<br>Fall Time | $V_{DD} = 250 \text{ V, } I_{D} = 6 \text{ A,}$ $R_{G} = 4.7 \Omega, V_{GS} = 10 \text{ V}$ (see Figure 15) |      | 20<br>10<br>19<br>8 |      | ns<br>ns<br>ns<br>ns |

| Q <sub>g</sub><br>Q <sub>gs</sub><br>Q <sub>gd</sub>                                                 | Total Gate Charge<br>Gate-Source Charge<br>Gate-Drain Charge        | $V_{DD} = 400 \text{ V, } I_{D} = 12 \text{ A,}$ $V_{GS} = 10 \text{ V}$ (see Figure 18)                    |      | 28<br>8<br>15       | 38   | nC<br>nC<br>nC       |

### **Table 8: Source Drain Diode**

| Symbol                                                 | Parameter                                                                    | Test Conditions                                                                                                              | Min. | Тур.                | Max.     | Unit          |

|--------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------|---------------------|----------|---------------|

| I <sub>SD</sub><br>I <sub>SDM</sub> (2)                | Source-drain Current<br>Source-drain Current (pulsed)                        |                                                                                                                              |      |                     | 14<br>56 | A<br>A        |

| V <sub>SD</sub> (1)                                    | Forward On Voltage                                                           | I <sub>SD</sub> = 12 A, V <sub>GS</sub> = 0                                                                                  |      |                     | 1.5      | V             |

| t <sub>rr</sub><br>Q <sub>rr</sub><br>I <sub>RRM</sub> | Reverse Recovery Time<br>Reverse Recovery Charge<br>Reverse Recovery Current | $I_{SD} = 12 \text{ A, di/dt} = 100 \text{ A/}\mu\text{s}$<br>$V_{DD} = 100 \text{V}$<br>(see Figure 16)                     |      | 270<br>2.23<br>16.5 |          | ns<br>µC<br>A |

| t <sub>rr</sub><br>Q <sub>rr</sub><br>I <sub>RRM</sub> | Reverse Recovery Time<br>Reverse Recovery Charge<br>Reverse Recovery Current | $I_{SD} = 12 \text{ A, di/dt} = 100 \text{ A/µs}$<br>$V_{DD} = 100 \text{ V, T}_j = 150 ^{\circ}\text{C}$<br>(see Figure 16) |      | 340<br>3<br>18      |          | ns<br>µC<br>A |

<sup>(1)</sup> Pulsed: Pulse duration = 300 μs, duty cycle 1.5 %.

(2) Pulse width limited by safe operating area.

(3) C<sub>oss eq.</sub> is defined as a constant equivalent capacitance giving the same charging time as C<sub>oss</sub> when V<sub>DS</sub> increases from 0 to 80% V<sub>DSS</sub>.