# STM32F103xC STM32F103xD STM32F103xE

High-density performance line ARM-based 32-bit MCU with 256 to 512KB Flash, USB, CAN, 11 timers, 3 ADCs, 13 communication interfaces

#### **Features**

- Core: ARM 32-bit Cortex<sup>TM</sup>-M3 CPU

- 72 MHz maximum frequency,

1.25 DMIPS/MHz (Dhrystone 2.1)

performance at 0 wait state memory

- Single-cycle multiplication and hardware division

#### ■ Memories

- 256 to 512 Kbytes of Flash memory

- up to 64 Kbytes of SRAM

- Flexible static memory controller with 4

Chip Select. Supports Compact Flash,

SRAM, PSRAM, NOR and NAND memories

- LCD parallel interface, 8080/6800 modes

- Clock, reset and supply management

- 2.0 to 3.6 V application supply and I/Os

- POR, PDR, and programmable voltage detector (PVD)

- 4-to-16 MHz crystal oscillator

- Internal 8 MHz factory-trimmed RC

- Internal 40 kHz RC with calibration

- 32 kHz oscillator for RTC with calibration

#### Low power

- Sleep, Stop and Standby modes

- V<sub>BAT</sub> supply for RTC and backup registers

- $3 \times 12$ -bit, 1 µs A/D converters (up to 21 channels)

- Conversion range: 0 to 3.6 V

- Triple-sample and hold capability

- Temperature sensor

- 2 × 12-bit D/A converters

- DMA: 12-channel DMA controller

- Supported peripherals: timers, ADCs, DAC, SDIO, I<sup>2</sup>Ss, SPIs, I<sup>2</sup>Cs and USARTs

- Debug mode

- Serial wire debug (SWD) & JTAG interfaces

- Cortex-M3 Embedded Trace Macrocell™

- Up to 112 fast I/O ports

- 51/80/112 I/Os, all mappable on 16 external interrupt vectors and almost all 5 V-tolerant

- Up to 11 timers

- Up to four 16-bit timers, each with up to 4 IC/OC/PWM or pulse counter and quadrature (incremental) encoder input

- 2 x 16-bit motor control PWM timers with dead-time generation and emergency stop

- 2 × watchdog timers (Independent and Window)

- SysTick timer: a 24-bit downcounter

- 2  $\times$  16-bit basic timers to drive the DAC

- Up to 13 communication interfaces

- Up to  $2 \times I^2C$  interfaces (SMBus/PMBus)

- Up to 5 USARTs (ISO 7816 interface, LIN, IrDA capability, modem control)

- Up to 3 SPIs (18 Mbit/s), 2 with I<sup>2</sup>S interface multiplexed

- CAN interface (2.0B Active)

- USB 2.0 full speed interface

- SDIO interface

- CRC calculation unit, 96-bit unique ID

- ECOPACK<sup>®</sup> packages

Table 1. Device summary

| Reference   | Part number                            |

|-------------|----------------------------------------|

| STM32F103xC | STM32F103RC STM32F103VC<br>STM32F103ZC |

| STM32F103xD | STM32F103RD STM32F103VD<br>STM32F103ZD |

| STM32F103xE | STM32F103RE STM32F103ZE<br>STM32F103VE |

## 5.2 Absolute maximum ratings

Table 7. Voltage characteristics

| Symbol                                | Ratings                                                                                             | Min                   | Max                   | Unit |

|---------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------|-----------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>      | $V_{DD}$ – $V_{SS}$ External main supply voltage (including $V_{DDA}$ and $V_{DD}$ ) <sup>(1)</sup> |                       | 4.0                   |      |

| V <sub>IN</sub> <sup>(2)</sup>        | Input voltage on five volt tolerant pin                                                             | V <sub>SS</sub> – 0.3 | V <sub>DD</sub> + 4.0 | V    |

|                                       | Input voltage on any other pin                                                                      | $V_{SS}-0.3$          | 4.0                   |      |

| l∆V <sub>DDx</sub> l                  | Variations between different V <sub>DD</sub> power pins                                             |                       | 50                    | mV   |

| IV <sub>SSX</sub> - V <sub>SS</sub> I | Variations between all the different ground pins                                                    |                       | 50                    | IIIV |

| V <sub>ESD(HBM)</sub>                 | Electrostatic discharge voltage (human body model)                                                  |                       |                       |      |

All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

Table 8. Current characteristics

| Symbol                               | Ratings                                                                                                   | Max.  | Unit |  |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------|-------|------|--|

| I <sub>VDD</sub>                     | I <sub>VDD</sub> Total current into V <sub>DD</sub> /V <sub>DDA</sub> power lines (source) <sup>(1)</sup> |       |      |  |

| l <sub>vss</sub>                     | Total current out of V <sub>SS</sub> ground lines (sink) <sup>(1)</sup>                                   | 150   |      |  |

| I <sub>IO</sub>                      | Output current sunk by any I/O and control pin                                                            | 25    |      |  |

|                                      | Output current source by any I/Os and control pin                                                         | - 25  | mA   |  |

| (2)                                  | Injected current on five volt tolerant pins <sup>(3)</sup>                                                | -5/+0 |      |  |

| I <sub>INJ(PIN)</sub> <sup>(2)</sup> | Injected current on any other pin <sup>(4)</sup>                                                          | ± 5   |      |  |

| ΣΙ <sub>ΙΝJ(PIN)</sub>               | Total injected current (sum of all I/O and control pins) <sup>(5)</sup>                                   | ± 25  |      |  |

All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

Table 9. Thermal characteristics

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to +150 | °C   |

| T <sub>J</sub>   | Maximum junction temperature | 150         | °C   |

## 5.3 Operating conditions

## 5.3.1 General operating conditions

Table 10. General operating conditions

| able 10.                        | General operating condition                                                            |                                      |     |     |      |

|---------------------------------|----------------------------------------------------------------------------------------|--------------------------------------|-----|-----|------|

| Symbol                          | Parameter                                                                              | Conditions                           | Min | Max | Unit |

| f <sub>HCLK</sub>               | Internal AHB clock frequency                                                           |                                      | 0   | 72  |      |

| f <sub>PCLK1</sub>              | Internal APB1 clock frequency                                                          |                                      | 0   | 36  | MHz  |

| f <sub>PCLK2</sub>              | Internal APB2 clock frequency                                                          |                                      | 0   | 72  |      |

| V <sub>DD</sub>                 | Standard operating voltage                                                             |                                      | 2   | 3.6 | V    |

| v (1)                           | Analog operating voltage (ADC not used)                                                | Must be the same potential           | 2   | 3.6 | V    |

| V <sub>DDA</sub> <sup>(1)</sup> | Analog operating voltage (ADC used)                                                    | as V <sub>DD</sub> <sup>(2)</sup>    |     | 3.6 | V    |

| $V_{BAT}$                       | Backup operating voltage                                                               |                                      | 1.8 | 3.6 | V    |

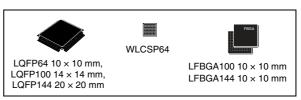

|                                 | Power dissipation at $T_A = 85$ °C for suffix 6 or $T_A = 105$ °C for suffix $7^{(3)}$ | LQFP144                              |     | 666 |      |

|                                 |                                                                                        | LQFP100                              |     | 434 | mW   |

| В                               |                                                                                        | LQFP64                               |     | 444 |      |

| $P_D$                           |                                                                                        | LFBGA100                             |     | 500 |      |

|                                 |                                                                                        | LFBGA144                             |     | 500 |      |

|                                 |                                                                                        | WLCSP64                              |     | 400 |      |

|                                 | Ambient temperature for 6                                                              | Maximum power dissipation            | -40 | 85  | °C   |

| Τ.                              | suffix version                                                                         | Low power dissipation <sup>(4)</sup> | -40 | 105 |      |

| TA                              | Ambient temperature for 7                                                              | Maximum power dissipation            | -40 | 105 | °C   |

|                                 | suffix version                                                                         | Low power dissipation <sup>(4)</sup> | -40 | 125 |      |

| т.                              | lunction temporature reserve                                                           | 6 suffix version                     | -40 | 105 | °C   |

| TJ                              | Junction temperature range                                                             | 7 suffix version                     | -40 | 125 | -0   |

## 5.3.2 Operating conditions at power-up / power-down

Table 11. Operating conditions at power-up / power-down

| Symbol           | Parameter                      | Conditions | Min | Max | Unit  |

|------------------|--------------------------------|------------|-----|-----|-------|

| t                | V <sub>DD</sub> rise time rate |            | 0   | ~   | μs/V  |

| t <sub>VDD</sub> | V <sub>DD</sub> fall time rate |            | 20  | 8   | μ5/ ν |

#### 5.3.3 Embedded reset and power control block characteristics

Table 12. Embedded reset and power control block characteristics

| Symbol                               | Parameter                                     | Conditions                  | Min                | Тур  | Max  | Unit |

|--------------------------------------|-----------------------------------------------|-----------------------------|--------------------|------|------|------|

|                                      |                                               | PLS[2:0]=000 (rising edge)  | 2.1                | 2.18 | 2.26 | V    |

|                                      |                                               | PLS[2:0]=000 (falling edge) | 2                  | 2.08 | 2.16 | V    |

|                                      |                                               | PLS[2:0]=001 (rising edge)  | 2.19               | 2.28 | 2.37 | V    |

|                                      |                                               | PLS[2:0]=001 (falling edge) | 2.09               | 2.18 | 2.27 | V    |

|                                      |                                               | PLS[2:0]=010 (rising edge)  | 2.28               | 2.38 | 2.48 | V    |

|                                      |                                               | PLS[2:0]=010 (falling edge) | 2.18               | 2.28 | 2.38 | V    |

|                                      |                                               | PLS[2:0]=011 (rising edge)  | 2.38               | 2.48 | 2.58 | V    |

| $V_{PVD}$                            | Programmable voltage detector level selection | PLS[2:0]=011 (falling edge) | 2.28               | 2.38 | 2.48 | V    |

| <b>V</b> PVD                         |                                               | PLS[2:0]=100 (rising edge)  | 2.47               | 2.58 | 2.69 | V    |

|                                      |                                               | PLS[2:0]=100 (falling edge) | 2.37               | 2.48 | 2.59 | V    |

|                                      |                                               | PLS[2:0]=101 (rising edge)  | 2.57               | 2.68 | 2.79 | V    |

|                                      |                                               | PLS[2:0]=101 (falling edge) | 2.47               | 2.58 | 2.69 | V    |

|                                      |                                               | PLS[2:0]=110 (rising edge)  | 2.66               | 2.78 | 2.9  | V    |

|                                      |                                               | PLS[2:0]=110 (falling edge) | 2.56               | 2.68 | 2.8  | V    |

|                                      |                                               | PLS[2:0]=111 (rising edge)  | 2.76               | 2.88 | 3    | V    |

|                                      |                                               | PLS[2:0]=111 (falling edge) | 2.66               | 2.78 | 2.9  | V    |

| V <sub>PVDhyst</sub> <sup>(2)</sup>  | PVD hysteresis                                |                             |                    | 100  |      | mV   |

| V                                    | Power on/power down                           | Falling edge                | 1.8 <sup>(1)</sup> | 1.88 | 1.96 | V    |

| V <sub>POR/PDR</sub>                 | reset threshold                               | Rising edge                 | 1.84               | 1.92 | 2.0  | V    |

| V <sub>PDRhyst</sub> <sup>(2)</sup>  | PDR hysteresis                                |                             |                    | 40   |      | mV   |

| T <sub>RSTTEMPO</sub> <sup>(2)</sup> | Reset temporization                           |                             | 1                  | 2.5  | 4.5  | mS   |

<sup>1.</sup> The product behavior is guaranteed by design down to the minimum  $V_{POR/PDR}$  value.

<sup>2.</sup> Guaranteed by design, not tested in production.

| Pe   | ripheral            | Typical consumption at 25 °C | Unit |

|------|---------------------|------------------------------|------|

|      | GPIOA               | 0.55                         |      |

|      | GPIOB               | 0.72                         |      |

|      | GPIOC               | 0.72                         |      |

|      | GPIOD               | 0.55                         |      |

|      | GPIOE               | 1                            |      |

|      | GPIOF               | 0.72                         |      |

| APB2 | GPIOG               | 1                            | mA   |

| APD2 | ADC1 <sup>(2)</sup> | 1.9                          | IIIA |

|      | ADC2                | 1.7                          |      |

|      | TIM1                | 1.8                          |      |

|      | SPI1                | 0.4                          |      |

|      | TIM8                | 1.7                          |      |

|      | USART1              | 0.9                          |      |

|      | ADC3                | 1.7                          |      |

Table 20. Peripheral current consumption<sup>(1)</sup> (continued)

#### 5.3.6 External clock source characteristics

#### High-speed external user clock generated from an external source

Table 21. High-speed external user clock characteristics

| Symbol                                                                | Parameter                                           | Conditions                       | Min                | Тур | Max                | Unit |

|-----------------------------------------------------------------------|-----------------------------------------------------|----------------------------------|--------------------|-----|--------------------|------|

| f <sub>HSE_ext</sub>                                                  | User external clock source frequency <sup>(1)</sup> |                                  | 1                  | 8   | 25                 | MHz  |

| V <sub>HSEH</sub>                                                     | OSC_IN input pin high level voltage                 |                                  | 0.7V <sub>DD</sub> |     | $V_{DD}$           | V    |

| V <sub>HSEL</sub>                                                     | OSC_IN input pin low level voltage                  |                                  | $V_{SS}$           |     | 0.3V <sub>DD</sub> | V    |

| $\begin{array}{c} t_{w(\text{HSE})} \\ t_{w(\text{HSE})} \end{array}$ | OSC_IN high or low time <sup>(1)</sup>              |                                  | 5                  |     |                    | ns   |

| t <sub>r(HSE)</sub>                                                   | OSC_IN rise or fall time <sup>(1)</sup>             |                                  |                    |     | 20                 | 115  |

| C <sub>in(HSE)</sub>                                                  | OSC_IN input capacitance <sup>(1)</sup>             |                                  |                    | 5   |                    | pF   |

| DuCy <sub>(HSE)</sub>                                                 | Duty cycle                                          |                                  | 45                 |     | 55                 | %    |

| ΙL                                                                    | OSC_IN Input leakage current                        | $V_{SS} \leq V_{IN} \leq V_{DD}$ |                    |     | ±1                 | μΑ   |

<sup>1.</sup> Guaranteed by design, not tested in production.

<sup>1.</sup>  $f_{HCLK} = 72$  MHz,  $f_{APB1} = f_{HCLK}/2$ ,  $f_{APB2} = f_{HCLK}$ , default prescaler value for each peripheral.

<sup>2.</sup> Specific conditions for ADC:  $f_{HCLK} = 56$  MHz,  $f_{APB1} = f_{HCLK}/2$ ,  $f_{APB2} = f_{HCLK}$ ,  $f_{ADCCLK} = f_{APB2/4}$ , ADON bit in the ADC\_CR2 register is set to 1.

#### Low-speed external user clock generated from an external source

Table 22. Low-speed external user clock characteristics

| Tubic LL.             | Low opeca external acer block offaracteriotics      |                               |                    |        |                    |      |

|-----------------------|-----------------------------------------------------|-------------------------------|--------------------|--------|--------------------|------|

| Symbol                | Parameter                                           | Conditions                    | Min                | Тур    | Max                | Unit |

| f <sub>LSE_ext</sub>  | User External clock source frequency <sup>(1)</sup> |                               |                    | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>     | OSC32_IN input pin high level voltage               |                               | 0.7V <sub>DD</sub> |        | V <sub>DD</sub>    | V    |

| V <sub>LSEL</sub>     | OSC32_IN input pin low level voltage                |                               | V <sub>SS</sub>    |        | 0.3V <sub>DD</sub> | V    |

| t <sub>w(LSE)</sub>   | OSC32_IN high or low time <sup>(1)</sup>            |                               | 450                |        |                    | ns   |

| t <sub>r(LSE)</sub>   | OSC32_IN rise or fall time <sup>(1)</sup>           |                               |                    |        | 50                 | 115  |

| C <sub>in(LSE)</sub>  | OSC32_IN input capacitance <sup>(1)</sup>           |                               |                    | 5      |                    | pF   |

| DuCy <sub>(LSE)</sub> | Duty cycle                                          |                               | 30                 |        | 70                 | %    |

| IL                    | OSC32_IN Input leakage current                      | $V_{SS} \le V_{IN} \le V_{D}$ |                    |        | ±1                 | μΑ   |

<sup>1.</sup> Guaranteed by design, not tested in production.

Figure 20. High-speed external clock source AC timing diagram

#### High-speed external clock generated from a crystal/ceramic resonator

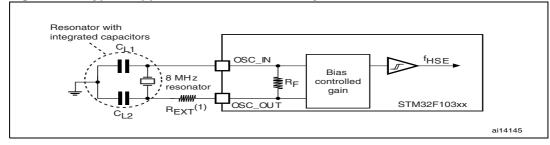

The high-speed external (HSE) clock can be supplied with a 4 to 16 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in . In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

|                                     | 1102 1 10 11112 00011111101 0111111010                                                                           |                                                                               |     |     |     |      |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----|-----|-----|------|

| Symbol                              | Parameter                                                                                                        | Conditions                                                                    | Min | Тур | Max | Unit |

| f <sub>OSC_IN</sub>                 | Oscillator frequency                                                                                             |                                                                               | 4   | 8   | 16  | MHz  |

| R <sub>F</sub>                      | Feedback resistor                                                                                                |                                                                               |     | 200 |     | kΩ   |

| С                                   | Recommended load capacitance versus equivalent serial resistance of the crystal (R <sub>S</sub> ) <sup>(3)</sup> | R <sub>S</sub> = 30 Ω                                                         |     | 30  |     | pF   |

| i <sub>2</sub>                      | HSE driving current                                                                                              | V <sub>DD</sub> = 3.3 V, V <sub>IN</sub> = V <sub>SS</sub><br>with 30 pF load |     |     | 1   | mA   |

| 9 <sub>m</sub>                      | Oscillator transconductance                                                                                      | Startup                                                                       | 25  |     |     | mA/V |

| t <sub>SU(HSE)</sub> <sup>(4)</sup> | Startup time                                                                                                     | V <sub>DD</sub> is stabilized                                                 |     | 2   |     | ms   |

Table 23. HSE 4-16 MHz oscillator characteristics<sup>(1)(2)</sup>

- 1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

- 2. Based on characterization results, not tested in production.

- The relatively low value of the RF resistor offers a good protection against issues resulting from use in a humid environment, due to the induced leakage and the bias condition change. However, it is recommended to take this point into account if the MCU is used in tough humidity conditions.

- t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see  $\,$ ).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ . Refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

Figure 22. Typical application with an 8 MHz crystal

1. R<sub>EXT</sub> value depends on the crystal characteristics.

## 5.3.14 I/O port characteristics

#### General input/output characteristics

Table 46. I/O static characteristics

| Symbol           | Parameter                                                           | Conditions                                      | Min                               | Тур | Мах                                | Unit |  |

|------------------|---------------------------------------------------------------------|-------------------------------------------------|-----------------------------------|-----|------------------------------------|------|--|

| V                | Standard IO input low level voltage                                 |                                                 | -0.3                              |     | 0.28*(V <sub>DD</sub> -2 V)+0.8 V  | V    |  |

| $V_{IL}$         | IO FT <sup>(1)</sup> input low level voltage                        |                                                 | -0.3                              |     | 0.32*(V <sub>DD</sub> -2 V)+0.75 V | V    |  |

|                  | Standard IO input high level voltage                                |                                                 | 0.41*(V <sub>DD</sub> -2 V)+1.3 V |     | V <sub>DD</sub> +0.3               | V    |  |

| $V_{IH}$         | IO FT <sup>(1)</sup> input high level                               | V <sub>DD</sub> > 2 V                           | 0.40*()/ 0.1/) +1.1/              |     | 5.5                                | V    |  |

|                  | voltage                                                             | $V_{DD} \le 2 V$                                | 0.42*(V <sub>DD</sub> -2 V)+1 V   |     | 5.2                                | V    |  |

| $V_{hys}$        | Standard IO Schmitt<br>trigger voltage<br>hysteresis <sup>(2)</sup> |                                                 | 200                               |     |                                    | mV   |  |

| .,,-             | IO FT Schmitt trigger<br>voltage hysteresis <sup>(2)</sup>          |                                                 | 5% V <sub>DD</sub> <sup>(3)</sup> |     |                                    | mV   |  |

| I <sub>lkg</sub> | Input leakage current (4)                                           | $V_{SS} \le V_{IN} \le V_{DD}$<br>Standard I/Os |                                   |     | ±1                                 | μA   |  |

| 3                |                                                                     | V <sub>IN</sub> = 5 V, I/O FT                   |                                   |     | 3                                  |      |  |

| R <sub>PU</sub>  | Weak pull-up equivalent resistor <sup>(5)</sup>                     | $V_{IN} = V_{SS}$                               | 30                                | 40  | 50                                 | kΩ   |  |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(5)</sup>                   | $V_{IN} = V_{DD}$                               | 30                                | 40  | 50                                 | kΩ   |  |

| C <sub>IO</sub>  | I/O pin capacitance                                                 |                                                 |                                   | 5   |                                    | pF   |  |

FT = Five-volt tolerant. In order to sustain a voltage higher than V<sub>DD</sub>+0.3 the internal pull-up/pull-down resistors must be disabled.

<sup>2.</sup> Hysteresis voltage between Schmitt trigger switching levels. Based on characterization, not tested in production.

<sup>3.</sup> With a minimum of 100 mV.

<sup>4.</sup> Leakage could be higher than max. if negative current is injected on adjacent pins.

Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This MOS/NMOS contribution to the series resistance is minimum (~10% order).

| Table 37. OOD DO electrical characteristics |                                      |                                          |                     |      |            |  |  |

|---------------------------------------------|--------------------------------------|------------------------------------------|---------------------|------|------------|--|--|

| Symbol                                      | Parameter                            | Min. <sup>(1)</sup>                      | Max. <sup>(1)</sup> | Unit |            |  |  |

| Input levels                                |                                      |                                          |                     |      |            |  |  |

| $V_{DD}$                                    | USB operating voltage <sup>(2)</sup> |                                          | 3.0 <sup>(3)</sup>  | 3.6  | ٧          |  |  |

| V <sub>DI</sub> <sup>(4)</sup>              | Differential input sensitivity       | I(USBDP, USBDM)                          | 0.2                 |      |            |  |  |

| V <sub>CM</sub> <sup>(4)</sup>              | Differential common mode range       | Includes V <sub>DI</sub> range           | 0.8                 | 2.5  | ٧          |  |  |

| V <sub>SE</sub> <sup>(4)</sup>              | Single ended receiver threshold      |                                          | 1.3                 | 2.0  |            |  |  |

| Output levels                               |                                      |                                          |                     |      |            |  |  |

| V <sub>OL</sub>                             | Static output level low              | $R_L$ of 1.5 k $\Omega$ to 3.6 $V^{(5)}$ |                     | 0.3  | V          |  |  |

| V <sub>OH</sub>                             | Static output level high             | $R_L$ of 15 k $\Omega$ to $V_{SS}^{(5)}$ | 2.8                 | 3.6  | ] <b>'</b> |  |  |

Table 57. USB DC electrical characteristics

- 1. All the voltages are measured from the local ground potential.

- 2. To be compliant with the USB 2.0 full-speed electrical specification, the USBDP (D+) pin should be pulled up with a 1.5 k $\Omega$  resistor to a 3.0-to-3.6 V voltage range.

- 3. The STM32F103xx USB functionality is ensured down to 2.7 V but not the full USB electrical characteristics which are degraded in the 2.7-to-3.0 V  $\rm V_{DD}$  voltage range.

- 4. Guaranteed by characterization, not tested in production.

- 5.  $R_L$  is the load connected on the USB drivers

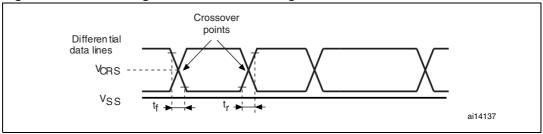

Figure 56. USB timings: definition of data signal rise and fall time

Table 58. USB: full-speed electrical characteristics

| Driver characteristics <sup>(1)</sup> |                                 |                                |     |     |      |  |  |

|---------------------------------------|---------------------------------|--------------------------------|-----|-----|------|--|--|

| Symbol                                | Parameter                       | Conditions                     | Min | Max | Unit |  |  |

| t <sub>r</sub>                        | Rise time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |

| t <sub>f</sub>                        | Fall Time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |

| t <sub>rfm</sub>                      | Rise/ fall time matching        | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %    |  |  |

| V <sub>CRS</sub>                      | Output signal crossover voltage |                                | 1.3 | 2.0 | V    |  |  |

- 1. Guaranteed by design, not tested in production.

- 2. Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification Chapter 7 (version 2.0).

#### 5.3.19 12-bit ADC characteristics

Note: It is recommended to perform a calibration after each power-up.

Table 59. ADC characteristics

| Symbol                           | Parameter                                 | Conditions                 | Min                                                                        | Тур                | Max                | Unit               |  |  |

|----------------------------------|-------------------------------------------|----------------------------|----------------------------------------------------------------------------|--------------------|--------------------|--------------------|--|--|

| $V_{DDA}$                        | Power supply                              |                            | 2.4                                                                        |                    | 3.6                | V                  |  |  |

| V <sub>REF+</sub>                | Positive reference voltage                |                            | 2.4                                                                        |                    | $V_{DDA}$          | V                  |  |  |

| I <sub>VREF</sub>                | Current on the V <sub>REF</sub> input pin |                            |                                                                            | 160 <sup>(1)</sup> | 220                | μΑ                 |  |  |

| f <sub>ADC</sub>                 | ADC clock frequency                       |                            | 0.6                                                                        |                    | 14                 | MHz                |  |  |

| f <sub>S</sub> <sup>(2)</sup>    | Sampling rate                             |                            | 0.05                                                                       |                    | 1                  | MHz                |  |  |

| f <sub>TRIG</sub> <sup>(2)</sup> | External trigger frequency                | f <sub>ADC</sub> = 14 MHz  |                                                                            |                    | 823                | kHz                |  |  |

| TRIG                             | External ingger frequency                 |                            |                                                                            |                    | 17                 | 1/f <sub>ADC</sub> |  |  |

| $V_{AIN}$                        | Conversion voltage range <sup>(3)</sup>   |                            | 0 (V <sub>SSA</sub> or V <sub>REF-</sub> tied to ground)                   |                    | V <sub>REF+</sub>  | V                  |  |  |

| R <sub>AIN</sub> <sup>(2)</sup>  | External input impedance                  |                            |                                                                            |                    | 50                 | kΩ                 |  |  |

| R <sub>ADC</sub> <sup>(2)</sup>  | Sampling switch resistance                |                            |                                                                            |                    | 1                  | kΩ                 |  |  |

| C <sub>ADC</sub> <sup>(2)</sup>  | Internal sample and hold capacitor        |                            |                                                                            |                    | 8                  | pF                 |  |  |

| <b>.</b> (2)                     | Calibration time                          | f <sub>ADC</sub> = 14 MHz  | 5.                                                                         | 5.9                |                    |                    |  |  |

| t <sub>CAL</sub> <sup>(2)</sup>  | Cambration time                           |                            | 83                                                                         |                    | 1/f <sub>ADC</sub> |                    |  |  |

| t <sub>lat</sub> (2)             | Injection trigger conversion              | f <sub>ADC</sub> = 14 MHz  |                                                                            |                    | 0.214              | μs                 |  |  |

| <sup>l</sup> lat` '              | latency                                   |                            |                                                                            |                    | 3 <sup>(4)</sup>   | 1/f <sub>ADC</sub> |  |  |

| <b>.</b> (2)                     | Regular trigger conversion latency        | $f_{ADC} = 14 \text{ MHz}$ |                                                                            |                    | 0.143              | μs                 |  |  |

| t <sub>latr</sub> (2)            |                                           |                            |                                                                            |                    | 2 <sup>(4)</sup>   | 1/f <sub>ADC</sub> |  |  |

| t <sub>S</sub> (2)               | Sampling time                             | f <sub>ADC</sub> = 14 MHz  | 0.107                                                                      |                    | 17.1               | μs                 |  |  |

| ī <sub>S</sub> '-'               |                                           |                            | 1.5                                                                        |                    | 239.5              | 1/f <sub>ADC</sub> |  |  |

| t <sub>STAB</sub> <sup>(2)</sup> | Power-up time                             |                            | 0                                                                          | 0                  | 1                  | μs                 |  |  |

|                                  | Total conversion time                     | $f_{ADC} = 14 \text{ MHz}$ | 1                                                                          |                    | 18                 | μs                 |  |  |

| t <sub>CONV</sub> <sup>(2)</sup> | (including sampling time)                 |                            | 14 to 252 (t <sub>S</sub> for sampling +12.5 for successive approximation) |                    |                    | 1/f <sub>ADC</sub> |  |  |

<sup>1.</sup> Based on characterization, not tested in production.

<sup>2.</sup> Guaranteed by design, not tested in production.

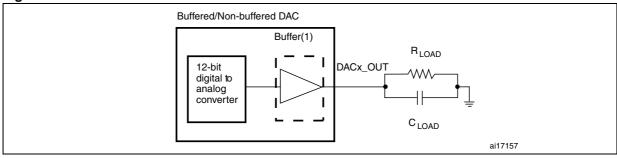

# 5.3.20 DAC electrical specifications

Table 63. DAC characteristics

| Symbol                           | Parameter                                                                                                                                                     | Min | Тур | Max                      | Unit | Comments                                                                                                               |  |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------------------|------|------------------------------------------------------------------------------------------------------------------------|--|

| $V_{DDA}$                        | Analog supply voltage                                                                                                                                         | 2.4 |     | 3.6                      | V    |                                                                                                                        |  |

| V <sub>REF+</sub>                | Reference supply voltage                                                                                                                                      | 2.4 |     | 3.6                      | ٧    | V <sub>REF+</sub> must always be below V <sub>DDA</sub>                                                                |  |

| V <sub>SSA</sub>                 | Ground                                                                                                                                                        | 0   |     | 0                        | V    |                                                                                                                        |  |

| R <sub>LOAD</sub> <sup>(1)</sup> | Resistive load with buffer ON                                                                                                                                 | 5   |     |                          | kΩ   |                                                                                                                        |  |

| R <sub>O</sub> <sup>(1)</sup>    | Impedance output with buffer<br>OFF                                                                                                                           |     |     | 15                       | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is 1.5 $M\Omega$ |  |

| C <sub>LOAD</sub> <sup>(1)</sup> | Capacitive load                                                                                                                                               |     |     | 50                       | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                        |  |

| DAC_OUT min <sup>(1)</sup>       | Lower DAC_OUT voltage with buffer ON                                                                                                                          | 0.2 |     |                          | V    | It gives the maximum output excursion of the DAC.  It corresponds to 12-bit input code                                 |  |

| DAC_OUT<br>max <sup>(1)</sup>    | Higher DAC_OUT voltage with buffer ON                                                                                                                         |     |     | V <sub>DDA</sub> – 0.2   | V    | (0x0E0) to (0xF1C) at $V_{REF+} = 3.6 \text{ V}$ and (0x155) and (0xEAB) at $V_{REF+} = 2.4 \text{ V}$                 |  |

| DAC_OUT min <sup>(1)</sup>       | Lower DAC_OUT voltage with buffer OFF                                                                                                                         |     | 0.5 |                          | mV   | It gives the maximum output                                                                                            |  |

| DAC_OUT max <sup>(1)</sup>       | Higher DAC_OUT voltage with buffer OFF                                                                                                                        |     |     | V <sub>REF+</sub> – 1LSB | ٧    | excursion of the DAC.                                                                                                  |  |

| I <sub>DDVREF+</sub>             | DAC DC current<br>consumption in quiescent<br>mode (Standby mode)                                                                                             |     |     | 220                      | μΑ   | With no load, worst code (0xF1C) at $V_{REF+} = 3.6 \text{ V}$ in terms of DC consumption on the inputs                |  |

|                                  | DAC DC current                                                                                                                                                |     |     | 380                      | μΑ   | With no load, middle code (0x800) on the inputs                                                                        |  |

| I <sub>DDA</sub>                 | consumption in quiescent mode (Standby mode)                                                                                                                  |     |     | 480                      | μΑ   | With no load, worst code (0xF1C) at $V_{REF+} = 3.6 \text{ V}$ in terms of DC consumption on the inputs                |  |

| DNL <sup>(2)</sup>               | Differential non linearity Difference between two consecutive code-1LSB)                                                                                      |     |     | ±0.5                     | LSB  | Given for the DAC in 10-bit configuration                                                                              |  |

|                                  |                                                                                                                                                               |     |     | ±2                       | LSB  | Given for the DAC in 12-bit configuration                                                                              |  |

|                                  | Integral non linearity<br>(difference between<br>measured value at Code i<br>and the value at Code i on a<br>line drawn between Code 0<br>and last Code 1023) |     |     | ±1                       | LSB  | Given for the DAC in 10-bit configuration                                                                              |  |

| INL <sup>(2)</sup>               |                                                                                                                                                               |     |     | ±4                       | LSB  | Given for the DAC in 12-bit configuration                                                                              |  |

Table 63. DAC characteristics (continued)

| Symbol                               | Parameter                                                                                                                                           | Min | Тур | Max  | Unit | Comments                                                                                                 |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|----------------------------------------------------------------------------------------------------------|

|                                      | Offset error (difference between measured value at Code (0x800) and the ideal value = V <sub>REF+</sub> /2)                                         |     |     | ±10  | mV   | Given for the DAC in 12-bit configuration                                                                |

| Offset <sup>(2)</sup>                |                                                                                                                                                     |     |     | ±3   | LSB  | Given for the DAC in 10-bit at V <sub>REF+</sub> = 3.6 V                                                 |

|                                      |                                                                                                                                                     |     |     | ±12  | LSB  | Given for the DAC in 12-bit at V <sub>REF+</sub> = 3.6 V                                                 |

| Gain<br>error <sup>(2)</sup>         | Gain error                                                                                                                                          |     |     | ±0.5 | %    | Given for the DAC in 12bit configuration                                                                 |

| t <sub>SETTLING</sub> <sup>(2)</sup> | Settling time (full scale: for a 10-bit input code transition between the lowest and the highest input codes when DAC_OUT reaches final value ±1LSB |     | 3   | 4    | μs   | $C_{LOAD} \leq 50$ pF, $R_{LOAD} \geq 5$ k $\Omega$                                                      |

| Update rate <sup>(2)</sup>           | Max frequency for a correct DAC_OUT change when small variation in the input code (from code i to i+1LSB)                                           |     |     | 1    | MS/s | $C_{LOAD} \le 50 \text{ pF, } R_{LOAD} \ge 5 \text{ k}\Omega$                                            |

| t <sub>WAKEUP</sub> (2)              | Wakeup time from off state (Setting the ENx bit in the DAC Control register)                                                                        |     | 6.5 | 10   | μs   | $C_{LOAD} \leq 50$ pF, $R_{LOAD} \geq 5$ k $\Omega$ input code between lowest and highest possible ones. |

| PSRR+ (1)                            | Power supply rejection ratio (to V <sub>DDA</sub> ) (static DC measurement                                                                          |     | -67 | -40  | dB   | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                         |

- 1. Guaranteed by design, not tested in production.

- 2. Guaranteed by characterization, not tested in production.

Figure 61. 12-bit buffered /non-buffered DAC

1. The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.