## Yixin **CMOS Quad 3-State R/S Latches**

High-Voltage Types (20-Volt Rating) Quad NOR R/S Latch - CD4043B Quad NAND R/S Latch - CD4044B

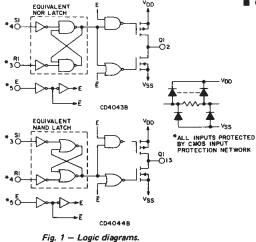

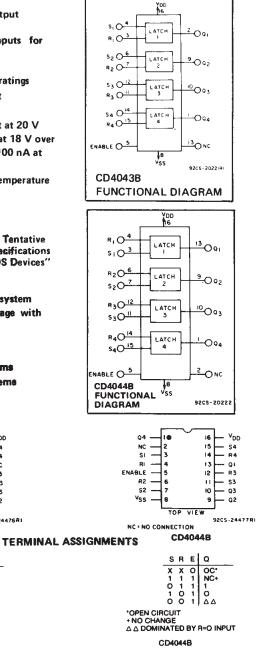

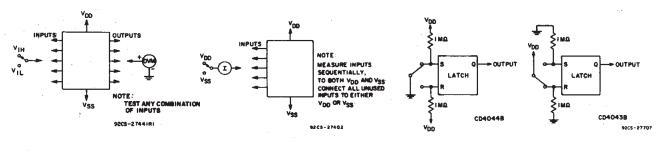

CD4043B types are guad crosscoupled 3-state CMOS NOR latches and the CD4044B types are quad cross-coupled 3state CMOS NAND latches. Each latch has a separate Q output and individual SET and RESET inputs. The Q outputs are controlled by a common ENABLE input. A logic "1" or high on the ENABLE input connects the latch states to the Q outputs. A logic "0" or low on the ENABLE input disconnects the latch states from the Q outputs, resulting in an open circuit condition on the Q outputs. The open circuit feature allows common busing of the outputs.

The CD4043B and CD4044B types are supplied in 16-lead hermetic dual-in-line ceramic packages (F3A suffix), 16-lead dual-in-line plastic packages (E suffix), 16-lead small-outline packages (D, DR, DT, DW, DWR, and NSR suffixes), and 16-lead thin shrink small-outline packages (PW and PWR suffixes).

#### MAXIMUM RATINGS, Absolute-Maximum Values:

| DC SUPPLY-VOLTAGE RANGE, (V <sub>DD</sub> )<br>Voltages referenced to V <sub>SS</sub> Terminal)0.5V to +20V         |

|---------------------------------------------------------------------------------------------------------------------|

| INPUT VOLTAGE RANGE, ALL INPUTS                                                                                     |

| DC INPUT CURRENT, ANY ONE INPUT                                                                                     |

| For T <sub>A</sub> = -55°C to +100°C                                                                                |

| For T <sub>A</sub> = +100°C to +125°C Derate Linearity at 12mW/°C to 200mW DEVICE DISSIPATION PER OUTPUT TRANSISTOR |

| FOR T <sub>A</sub> = FULL PACKAGE-TEMPERATURE RANGE (All Package Types)                                             |

| OPERATING-TEMPERATURE RANGE (T <sub>A</sub> )                                                                       |

| STORAGE TEMPERATURE RANGE (T <sub>stg</sub> )65°C to +150°C<br>LEAD TEMPERATURE (DURING SOLDERING):                 |

| At distance 1/16 ± 1/32 inch (1.59 ± 0.79mm) from case for 10s max                                                  |

# CD4043B, CD4044B Types

#### Features:

- 3-state outputs with common output ENABLE

- Separate SET and RESET inputs for each latch

- NOR and NAND configurations

- 5-V, 10-V, and 15-V parametric ratings

- Standardized symmetrical output characteristics

- 100% tested for guiescent current at 20 V

- Maximum input current of 1 µA at 18 V over full package temperature range; 100 nA at 18 V and 25°C

- Noise margin (over full package temperature range):  $1 V \text{ at } V_{DD} = 5 V$ 2 V at V<sub>DD</sub> = 10 V 2.5 V at V<sub>DD</sub> = 15 V

- Meets all requirements of JEDEC Tentative Standard No. 138, "Standard Specifications for Description of 'B' Series CMOS Devices'

Applications:

- Holding register in multi-register system

- Four bits of independent storage with

- output ENABLE

- Strobed register

- General digital logic

- CD4043B for positive logic systems

04

Q1

R١

\$2

R2

Vss

NC=NO CONNECTION

OPEN CIRCUIT

+ NO CHANGE △ DOMINATED BY S=1 INPUT CD4043B

ENABLE

■ CD4044B for negative logic systems

V00

R4

R3

02

92CS-24476R1

15

14 - S4 13 NC

12 - S3

10 - 03

OC\*

1 0 4

TOP VIEW

CD4043B

SREI Q

Ó 1

#### **TRUTH TABLES**

Recommended Operating Conditions TA=25°C For maximum reliability, nominal operating conditions should be selected so that operation is always within the following ranges.

| Characteristic 🤲                                                             | V <sub>DD</sub><br>(V) | Min.            | Max. | Units |

|------------------------------------------------------------------------------|------------------------|-----------------|------|-------|

| Supply-Voltage Range<br>(T <sub>A</sub> = Full Package<br>Temperature Range) | 1                      | 3               | 18   | v     |

| SET or RESET<br>Pulse Width, t <sub>W</sub>                                  | 5<br>10<br>15          | 160<br>80<br>40 | -    | ns    |

### **STATIC ELECTRICAL CHARACTERISTICS**

| CHARACTER-<br>ISTIC                            | CONDITIONS |      |     | LIM   | IITS AT | INDICAT | ED TEN | MPERATURES (°C) |                  |      | UNITS |  |  |  |

|------------------------------------------------|------------|------|-----|-------|---------|---------|--------|-----------------|------------------|------|-------|--|--|--|

|                                                | Vo         | VIN  | VDD |       |         |         |        | +25             |                  |      |       |  |  |  |

|                                                | (V)        | (V)  | (V) | 55    | -40     | +85     | +125   | Min.            | Тур.             | Max. |       |  |  |  |

| Quiescent Device<br>Current,<br>IDD Max.       | -          | 0,5  | 5   | 1     | 1       | 30      | 30     | -               | 0.02             | 1    | μΑ    |  |  |  |

|                                                | _          | 0,10 | 10  | 2     | 2       | 60      | 60     | -               | 0.02             | 2    |       |  |  |  |

|                                                | -          | 0,15 | 15  | 4     | 4       | 120     | 120    | -               | 0.02             | 4    |       |  |  |  |

|                                                | -          | 0,20 | 20  | 20    | 20      | 600     | 600    | -               | 0.04             | 20   |       |  |  |  |

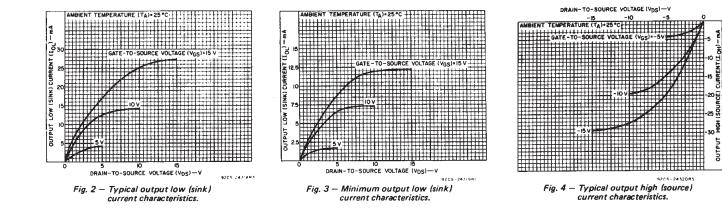

| Output Low                                     | 0.4        | 0,5  | 5   | 0.64  | 0.61    | 0.42    | 0.36   | 0.51            | 1                |      |       |  |  |  |

| (Sink) Current                                 | 0.5        | 0,10 | 10  | 1.6   | 1.5     | 1.1     | 0.9    | 1.3             | 2.6              | _    |       |  |  |  |

| IOL Min.                                       | 1.5        | 0,15 | 15  | 4.2   | 4       | 2.8     | 2.4    | 3.4             | 6.8              | _    |       |  |  |  |

| Output High                                    | 4.6        | 0,5  | 5   | -0.64 | -0.61   | -0.42   | -0.36  | -0.51           | -1               | -    | mA    |  |  |  |

| (Source)                                       | 2.5        | 0,5  | 5   | 2     | -1.8    | -1.3    | -1.15  | -1.6            | -3.2             | -    |       |  |  |  |

| Current,                                       | 9.5        | 0,10 | 10  | -1.6  | -1.5    | -1.1    | -0.9   | -1.3            | -2.6             | _    |       |  |  |  |

| IOH Min.                                       | 13.5       | 0,15 | 15  | -4.2  | -4      | -2.8    | -2.4   | -3.4            | -6.8             | _    |       |  |  |  |

| Output Voltage:                                | -          | 0,5  | 5   |       | 0       | .05     |        | -               | 0                | 0.05 |       |  |  |  |

| Low-Level,                                     |            | 0,10 | 10  | 0.05  |         |         |        | -               | 0                | 0.05 | v     |  |  |  |

| VOL Max.                                       |            | 0,15 | 15  | 0.05  |         |         |        | -               | 0                | 0.05 |       |  |  |  |

| Output Voltage:                                | _          | 0,5  | 5   | 4.95  |         |         | 4.95   | 5               | -                |      |       |  |  |  |

| High-Level,<br>VOH Min.                        | _          | 0,10 | 10  | 9.95  |         |         |        | 9.95            | 10               | _    |       |  |  |  |

|                                                | —          | 0,15 | 15  | 14.95 |         |         |        | 14.95           | 15               | -    |       |  |  |  |

| Input Low<br>Voltage,<br>VIL Max.              | 0.5, 4.5   | -    | 5   | 1.5   |         |         |        | -               | _                | 1.5  |       |  |  |  |

|                                                | 1, 9       | -    | 10  | 3     |         |         |        |                 | —                | 3    |       |  |  |  |

|                                                | 1.5,13.5   | -    | 15  | 4     |         |         |        | _               |                  | 4    |       |  |  |  |

| Input High<br>Voltage,<br>VIH Min.             | 0.5, 4.5   | -    | 5   | 3.5   |         |         |        | 3.5             | _                | —    | ▼.    |  |  |  |

|                                                | 1, 9       | -    | 10  | 7     |         |         |        | 7               | -                | _    | -     |  |  |  |

|                                                | 1.5, 3.5   | -    | 15  | 11    |         |         |        | 11              |                  | -    |       |  |  |  |

| Input Current<br>IIN Max.                      | _          | 0,18 | 18  | ±0.1  | ±0.1    | ±1      | ±1     | -               | ±10 <sup>5</sup> | ±0.1 | μΑ    |  |  |  |

| 3-State Output<br>Leakage Current<br>IOUT Max. | 0,18       | 0,18 | 18  | ±0.4  | ±0.4    | ±12     | ±12    | _               | ±10-4            | ±0.4 | μΑ    |  |  |  |

Ē

3

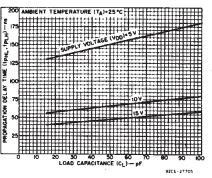

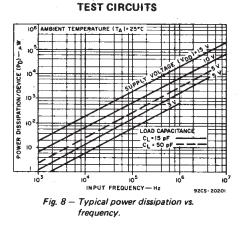

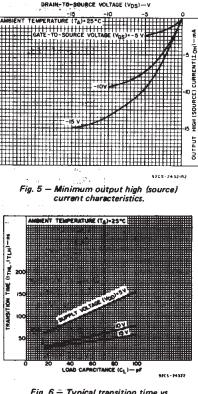

## **DYNAMIC ELECTRICAL CHARACTERISTICS** at $T_A = 25^{\circ}$ C; Input $t_r$ , $t_f = 20$ ns, $C_L = 50 \, pF$ , $R_L = 200 \, K\Omega$

| CHARACTERISTIC                                   |   | V <sub>DD</sub><br>(V) | ALL  | UNITS |     |

|--------------------------------------------------|---|------------------------|------|-------|-----|

|                                                  | а |                        | TYP. | MAX.  | 1   |

| Propagation Delay                                |   | 5                      | 150  | 300   |     |

| Time: tpHL, tpLH                                 |   | - 10                   | 70   | 140   | ris |

| SET or RESET to Q                                |   | 15                     | 50   | 100   |     |

| 3-State Propagation Delay                        |   | 5                      | 115  | 230   |     |

| Time: ENABLE to Q                                |   | 10                     | 55   | 110   | ns  |

| tPHZ, tPZH                                       |   | 15                     | 40   | 80    |     |

|                                                  |   | 5                      | 90   | 180   |     |

| tPLZ, tPZL                                       |   | 10                     | 50   | 100   | ns  |

|                                                  |   | 15                     | 35   | 70    |     |

| Transition Time:                                 |   | 5                      | 100  | 200   |     |

| tTHL, tTLH                                       |   | 10                     | 50   | 100   | ns  |

|                                                  | 1 | 15                     | 40   | 80    |     |

| Minimum                                          |   | 5                      | 80   | 160   | [   |

| SET or RESET                                     |   | 10                     | 40   | 80    | ns  |

| Pulse Width, t <sub>W</sub>                      |   | 15                     | 20   | 40    |     |

| nput Capacitance,<br>(Any Input) C <sub>IN</sub> |   |                        | 5    | 7.5   | pF  |

Fig. 7 — Typical propagation delay time vs. load capacitance—SET, RESET to Q, Q.

Fig. 6 — Typical transition time vs. load capacitance.

Fig. 9 - Quiescent device current.

Fig. 10 — Input voltage.

Fig. 11 - Input current.

Fig. 12 - Switch bounce eliminator.