来源:壹芯微 发布日期

2022-01-14 浏览:-

来源:壹芯微 发布日期

2022-01-14 浏览:-基于分布式算法的低通FIR滤波器设计介绍

传统数字滤波器硬件的实现主要采用专用集成电路(ASIC)和数字信号处理器(DSP)来实现。FPGA内部的功能块中采用了SRAM的查找表(lo-okuptable,LUT)结构,这种结构特别适用于并行处理结构,相对于传统方法来说,其并行度和扩展性都很好,它逐渐成为构造可编程高性能算法结构的新选择。

分布式算法是一种适合FPGA设计的乘加运算,由于FPGA中硬件乘法器资源有限,直接应运乘法会消耗大量的资源。本文利用了丰富的存储器资源进行查找表运算,设计了一种基于分布式算法低通FIR滤波器;利用线性相位FIR滤波器的对称性减小了硬件规模,采用了分割查找表技术,节省了FPGA硬件资源,并采用并行分布式算法结构和流水线技术提高了滤波器的速度,在FPGA上实现了该滤波器。

1.分布式的滤波器算法

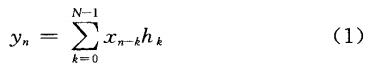

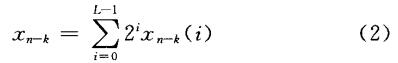

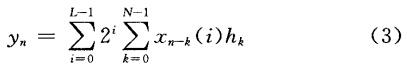

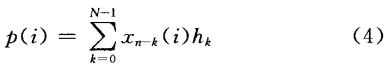

FIR滤波器突出的特点是单位取样响应h(n)仅有有限个非零值。对于一个N阶的FIR滤波器形式如下:

在许多数字信号处理应用领域中,在技术上是不需要通用的乘法算法的。对于本系统可以通过Matlab中的fdatool工具根据设计要求设计出滤波器的系统函数h(n),那么乘积项h(k)×x(n-k)就变成了2个常数的乘法。无符号数的分布式算法和有符号数的分布式算法是分布式算法在FIR滤波器中的2种典型算法。

1.1无符号数的分布式算法设计

由于FPGA为并行处理结构,所以假设x(n-k)数据宽度为Lb,则由式(1)可表示为:

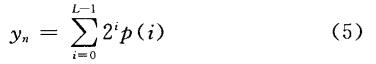

由式(1)、式(2)可以得到:

假设:

则式(1)可以表示为:

1.2有符号数的分布式算法设计

对于有符号数的补码表示为:

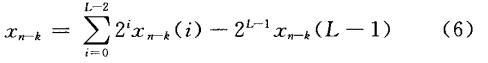

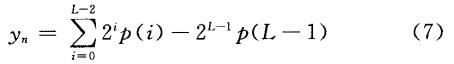

则由式(5),式(1)可得:

2.分布式的滤波器的软件实现

从式(5)和式(7)可以看出,利用分布式算法实现一个N项乘积和,关键是如何实现式(4)中乘积项及各乘积项之和。

在FPGA中可以预先设定一个N位输入的查找表来实现部分乘积项,即预先设定N阶滤波系统查找表,实现向量x(i)={x0(i),x1(i),x2(i),…,xN-1(i))到p(i)的一个映射。由于查找表的地址空间与阶数成指数关系(2N),完全用查找表来实现部分乘积项需要容量很大的存储器,这就需要占用巨大的资源,而且功耗增加、速度降低。因此为了减小设计规模,可以将一个大的查找表分为几个较小的查找表来实现。例如,本系统采用的8阶FIR滤波器,则用一个查找表来实现需要256(28)位地址空间的ROM,将8阶FIR滤波器分成两个4阶FIR滤波器实现,只需要2个16(24)位地址空间的ROM,这样大大地降低了设计规模和资源使用量。把输入x(i)作为地址,分为高四位和低四位地址进行查找。表1给出了8阶滤波系统的低四位地址x(i)与p(i)的映射关系。

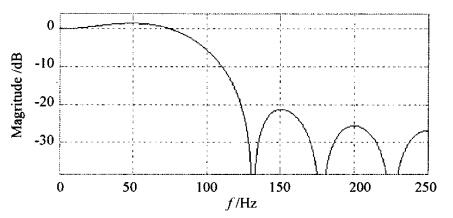

本系统中滤波器系统函数采用Matlab中的fdatool工具,并根据设计要求采用了kaiser窗设计出滤波器的系统函数h(n),其采样频率为500kHz,通频带带宽为100Hz。设计的低通滤波器如图1所示。若需实现高通或带通滤波器,只需在设计时利用高通或带通滤波器代替低通滤波器即可。

图1低通滤波器

利用Verilog硬件描述语言设计本系统软件,系统主要分为以下4个部分。包括顶层文件、A/D采样、算法实现和D/A转换。系统总体结构如图2所示。

图2系统整体框图

由于FPGA频率为100MHz,采用的DAC0809转换频率必须小于1MHz,所以在顶层文件对系统时钟进行200分频,提供外围所需时钟。然后对各模块进行例化,使之成为完整的系统。

对A/D采样输入3位地址,并使ALE=1,将地址存入地址锁存器中。此地址经译码选通8路模拟输入之一到比较器。START上升沿将逐次逼近寄存器复位。下降沿时启动A/D转换,之后EOC输出信号变低,指示转换正在进行。直到完成A/D转换,EOC变为高电平,指示A/D转换结束,结果数据已存入锁存器,这个信号可用作中断申请。当OE输入高电平时,输出三态门打开,转换结果的数字量输出到数据总线上。CLK为时钟输入信号线。由顶层文件的分频时钟提供500kHz时钟,对信号进行采集。

算法主体的实现主要由以下几个部分组成:数据接收存储、数据选择器、2个存储器、加法和控制部分。

数据接收是在每个时钟下降沿时检测转换完成信号,如果完成,则存入对应的存储器中,对于N阶的系统,就需要存储N个数据等待处理。然后利用数据选择器依次选择各个数据,对数据的每一位进行检测和提取,组成算法中所需要的数据。在控制信号的作用下利用累加器对数据叠加、移位处理即可实现。

最后,FPGA向DAC0832的数据输入口(D10~D17)输送数据。提供DAC0832数据锁存允许控制信号ILE,高电平有效。提供DAC0832控制信号(CS:片选信号;Xfer:数据传输控制信号;WRl、WR2:DAC寄存器写选通信号),低电平有效。

3.仿真实验、工况信号测试实验

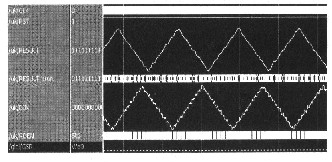

基于分布式算法低通FIR滤波器选用Xilinx公司的Virtex-Ⅱpro器件,在ISEl0.1下进行设计。利用modelsim6.5对滤波器进行仿真。系统采用频率为500kHz的分频时钟,在FPGA中产生一个高频方波和一个低频锯齿波信号,并对两个信号进行叠加。叠加后的信号作为输入,对应图中DIN,经过系统处理后输出结果对应图中RESULT,仿真结果如图3所示。

图3软件仿真

由图3中可以看出,本系统存在相位偏移和滤波后依然存在杂波信号的缺点,相位偏移主要是由滤波处理滞后于输入引起的,比较稳定且偏移较小,一般情况下可以忽略;杂波信号由系统阶数较低和系数量化误差引起的。实际应用中可根据情况选择适当阶数的滤波器和提高采样频率予以解决。

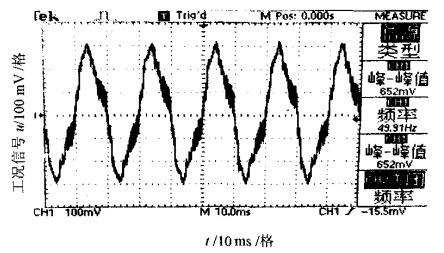

工况信号测试实验。由信号发生器同时产生一个50Hz低频信号和一个5kHz高频信号,然后对两个信号进行叠加,作为被测的工况信号。被测的工况信号经过A/D转换、滤波处理、D/A转换,然后在示波器中显示,如图4所示。输出波形中过滤掉了高频信号部分,同时低频信号能够通过该滤波器。由图4中可以看出,滤波处理后与实际信号还存在一定的误差。误差主要是由于算法中采用了低阶滤波器、系数量化误差、器件精度低等原因所致,该误差可以控制在允许范围,还可以通过选择高精度的器件和增加滤波器的阶数得以提高。

实际测试

图4实际测试

结语

本文总结了基于分布式算法的低通FIR滤波器设计方案,经实验结果表明,该滤波器工作可靠,滤波精度较高,且具有占用资源少,运算速度快。在资源允许的条件下可根据实际应用任意确定滤波器的字长和阶数,在高速数字信号处理领域可以得到很好的应用。

〔壹芯微〕专业研发生产二极管,三极管,MOS管,桥堆,专注领域,专业品质,研发技术-芯片源自中国台湾,拥有全工序封装生产线,配备高标准可靠性实验室,引入国外先进测试仪器,检测设备,以及专业团队丰富的生产经验,保障每个器件的参数和性能的充分稳定性,同时实现了高度全自动化生产,大幅度降低人工成本,并与中国台湾芯片制造商达成合作,产品低于同行10%,壹芯微还提供有选型替代,技术支持,售后FAE,欢迎点击页面右侧"在线客服" 咨询了解产品详情和最新报价,提供免费样品送予测试

手机号/微信:13534146615

QQ:2881579535

工厂地址:安徽省六安市金寨产业园区

深圳办事处地址:深圳市福田区宝华大厦A1428

中山办事处地址:中山市古镇长安灯饰配件城C栋11卡

杭州办事处:杭州市西湖区文三西路118号杭州电子商务大厦6层B座

电话:13534146615

企业QQ:2881579535

深圳市壹芯微科技有限公司 版权所有 | 备案号:粤ICP备2020121154号